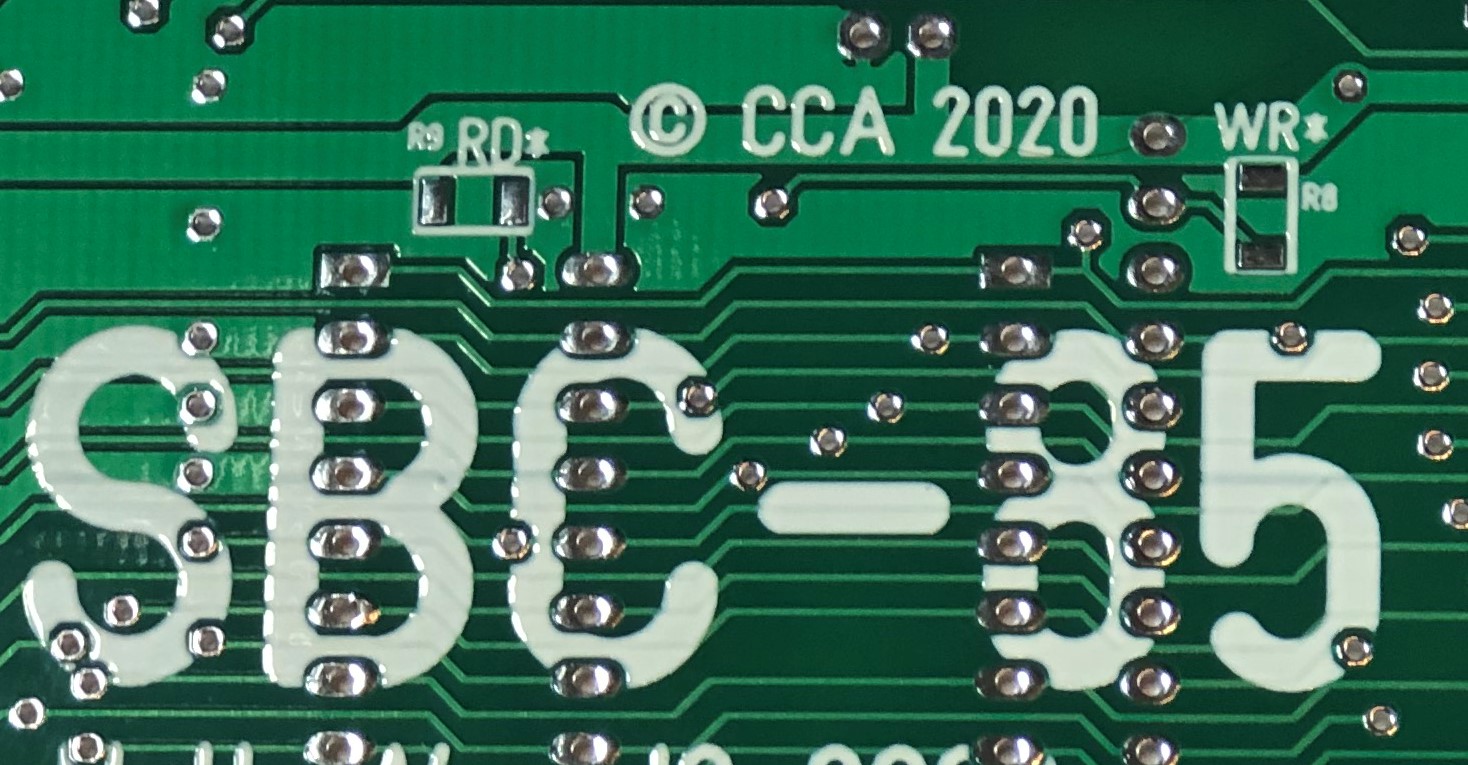

You may question the need for the R8 and R9 pull-up resistors on the RD* and WR* signals. These signals are tightly controlled by the 8085 and therefore it would seem that pull-up resistors are not necessary. However, these signals are, in fact, tri-stated under three conditions when the 8085 lets them go. First, when the HOLD line on the 8085 becomes active, this indicates that another system controller (e.g., another CPU or a DMA controller) wants to become the master. In response the 8085 relinquishes control, takes the Hold Acknowledge (HLDA) active, and puts the RD* and WR* into high-impedance. Between the time that this 8085 lets go of the RD* and WR* and the new master controller picks them up, these two signals are not driven and have a completely unknown state. Any component that happens to see an address match, however transient it may be, when a spurious RD* or WR* noise comes along that component will accept it as a valid state condition and bring data onto the bus or write data into memory or ports.

The second situation that puts the RD* and WR* into high impedance is when the CPU receives a HALT instruction. There are only two ways the processor can get out of the HALT condition: a system reset or when a valid interrupt occurs.

The third condition that RD* and WR* are tri-stated is during the first T-state after the RESETIN* goes is active.

In all of these cases, for system integrity it is crucial that the WR* line does not cause and unintended memory writes when released by the 8085.